SPI

– Serial Peripheral Interface is a bus interface used in many peripheral

devices and nowadays almost all microcontrollers have it. Basically it connects

a single masters to multiple slaves. So a single master controller can receive

and transmit data to multiple slave microcontrollers.

SPI

devices uses only 2 pins for data transfer MOSI (Master Out Slave In) and MISO

(Master In Slave Out). This reduction in pin reduces both power consumption and

package size. It also has SCK (Serial

Clock) and SS (Slave Select).

Pins

|

Equivalent Pins

|

Function

|

SDI (Serial Data In)

|

MOSI (Master Out Slave

In)

|

Serial Data into Slave

or Serial Data from Master

|

SDO (Serial Data Out)

|

MISO (Master In Slave

Out)

|

Serial Data from Slave

or Serial Data into Master

|

SCLK (Shift Clock)

|

SCK (Serial Clock)

|

To synchronize connected

devices

|

CE (Chip Enable)

|

SS (Slave Select)

|

Used initiate or

terminate the data transfer.

|

SPI Architecture

SPI

Consists of 2 shift registers, one in the master and the other in the slave

side. There is a clock generator in the master side that generates the clock

for both the shift registers.

|

| SPI Architecture |

As

shown in the figure, the serial out pin of the master is connected to the

serial in pin of the slave shift register by MOSI (Master Out Slave In), and

the serial input pin of the master is connected to the serial output pin of the

slave through MISO (Master In Slave Out). The SPI clock generator in the master

provides the required clock pulses to both the master’s and slave’s shift

registers. The clock input can be falling – or rising edge triggered.

In

SPI the shift registers are 8 bit long meaning 8 clock pulses required to

transfer the data between the two registers. SPI is a full duplex, meaning that

it sends and receives data simultaneously. Whenever the master wants to send

the data to the slave it transfers the data into the shift registers and

generates 8 clock pulses and after 8 clock pulses the data is transferred into

the slave. Similarly when the master

wants to receive the data the slave puts the data into the shift registers and

after 8 clock pulses the data is transferred from slave to the master.

The

SCK clock signal is used to synchronize the data transfer between the master

and the slave with the most significant bit (MSB) being transferred first.

During the transfer the SS stays high fir the while duration. The data is

transferred immediately after the address.

The

clock polarity and the clock phase are the two important aspects in the SPI

communication. The bit value of the Clock Polarity bit (CPOL) determines the

base value of the clock and the bit value of the Clock Phase bit (CPHA)

determines whether the change should happen on a rising edge or on a falling

edge.

CPOL

|

CPHA

|

Data Read and Change Time

|

SPI Mode

|

0

|

0

|

Read on the rising edge, change on the falling edge

|

0

|

0

|

1

|

Read

on the falling edge, change on the rising edge

|

1

|

1

|

0

|

Read on the falling edge, change on the rising edge

|

2

|

1

|

1

|

Read

on the rising edge, change on the falling edge

|

3

|

CPOL

= 0 CPHA = 0

|

| Timing Diagram with CPOL = 0 and CPHA = 0 |

CPOL

= 0 CPHA = 1

| Timing Diagram with CPOL = 0 and CPHA = 1 |

CPOL

= 1 CPHA = 0

| Timing Diagram with CPOL = 1 and CPHA = 0 |

CPOL

= 1 CPHA = 1

|

| Timing Diagram with CPOL = 1 and CPHA = 1 |

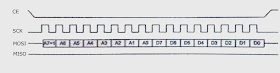

Writing Data to SPI Devices

2 modes of operation single byte write and multi byte

burst write

Single Byte Write

Following steps are used for writing data in a

single byte mode.

- Make CE = 0 to begin writing

- 8 bit address is shifted first 1 bit at a time with each edge of SCK. A7 = 1 in write mode and it goes in first. After all 8 bit address is sent in, the SPI device expects to receive the data belonging to that address location immediately.

- Again in a similar way the 8 bit data is shifted with 1 bit at a time with each edge of the SCK.

- Make CE = 1 to indicate the end of write cycle.

|

| Timing Diagram Single Byte Write Operation |

Multibyte burst write

Burst mode writing is an effective way to write

consecutive location. In this we provide the address of the first location,

followed by the data for the location. From this point on while the CE = 0 the

SPI device automatically increments the address location. Following steps are

used to achieve this.

- Make CE = 0 to begin writing.

- The 8 bit address is provided and shifted in, one bit at a time. The A7 = 1 for the write operation and the A7 bit goes in first.

- The 8 bit data for the first location is provided and shifted in. From then on we simply provide the consecutive data bytes to be placed in consecutive memory location. In the process the CE must be equal to 0.

- Make CE = 1 to end writing.

| Timing Diagram Multi Byte Write Operation |

Reading data from the SPI devices

Again we have 2 modes of operation. Single byte read

and multi byte burst read.

Single Byte Read

Following steps are used to get data from the SPI devices.- Make CE = 0 to start reading.

- The 8 bit address is shifted 1 bit at a time. A7 = 0 for read operation and A7 goes in first.

- After the transfer of 8 bit address to the SPI device the device that received the address sends out the data corresponding to the address location.

- Make CE = 1 to end the reading operation.

|

| Timing Diagram Single Byte Read Operation |

Multi Byte burst Read

Burst mode is an effective way to read the

consecutive set of data from the device. In this we provide the address of the

first data. From then on while CE = 0, the consecutive bytes from the

consecutive memory location are brought out from the device. SPI device

internally increments the address location while CE = 0. Following steps are used

to get multiple bytes of data from consecutive location.

- Make CE = 0 to start reading.

- The address of the first location is provided and shifted in. For this A7 = 0 for reading operation and the A7 bit goes in first.

- The data for the first location is shifted out with each clock. From then on, we simply keep getting consecutive data from the consecutive location. In this process the CE should remain low.

- Make CE = 1 to end reading.

| |||

| Timing Diagram Multi Byte Read Operation |

No comments:

Post a Comment